条件に該当する製品248件

-

FMC213 – FMC Quad ADC 16-bit @ 250 MSPS, DAC 14-bit @ 5.7 GSPS

VadaTech アナログI/O FMC 物理 天体・FPGA Mezzanine Card (FMC) per VITA 57 ・Quad ADC based on ADS42JB69 ・DAC based on AD9129 ・RF front panel reference clock input ・RoHS compliant

-

FMC215 – FMC ADC 12-bit @ 4.0 GSPS, DAC 12-bit @ 4.5 GSPS

VadaTech アナログI/O FMC 物理 天体・FPGA Mezzanine Card (FMC) per VITA 57 ・TI ADC12J4000 ADC ・E2V EV12DS400 DAC ・Excellent dynamic performance ・Front panel interface includes CLK In, Trig In, AnalogIn/Out, and GPIO ・Ultra Low-Noise wide-band PLL ・On-chip delay locked loops (DLLs) optimize timing between different clock domains.

-

PMC-E2001 100KSPS 16b ADC/DAC PMC

Curtiss-Wright アナログI/O PMC/XMC 防衛 生産中止品(EOL)・16 Channels Delta Sigma Analog Output - up to 108 kHz output sampling rate ・4 Channels Analog Input - 96ksps sample rate ・All channels 16-bit resolution ・Factory configurable input voltages ・Comprehensive Built-in-Test, BIT ・Commercial and rugged conduction-cooled environmental versions

-

16AIO88(The PMC-16AIO88 is a versatile Multifunction analog I/O board. The board has 8 analog inputs and 8 analog outputs per board, and supports arbitrary waveform generation. A single 16-Bit scanning Analog-to-Digital

GneralStandardsCorporation アナログI/O PMC/XMC 試験 環境The PMC-16AIO88 is a versatile Multifunction analog I/O board. The board has 8 analog inputs and 8 analog outputs per board, and supports arbitrary waveform generation. A single 16-Bit scanning Analog-to-Digital converter scans 8 single-ended or 4 differential inputs at an aggregate rate of 72,500 samples per second into the 32,000-sample storage FIFO. Up to 250,000 samples per second aggregate output update rates for the 8 D/A channels. Analog outputs are double-buffered and allow for software or hardware (Synchronized) strobes for output updating. I/O ranges are ±2.5, ±5.0, and ±10.0 volts. Output FIFO buffers provide up to 16,000-sample capacity. Advanced features include: Loopback for Built-in-Test support, automatic calibration, continuous or burst input scanning modes, and runtime calibration trimming implemented in hardware, without Host CPU intervention

-

FMC-520 Quad 550MSPS/Dual 1GSPS 16b DAC FMC

Curtiss-Wright アナログI/O FMC 防衛・Quad Channel 500 MSPS or dual channel 1GSPS, 16-bit DAC FPGA Mezzanine Card (FMC) ・Two Texas Instruments DAC5682Z, 16-bit DACs ・Up to 500 MSPS using 4 channels ・Up to 1000 MSPS using 2 channels ・AC coupled analog output bandwidth 775MHz ・Choice of onboard and external clocks sources ・Multi-board synchronization capability ・FMC/VITA 57 form factor ・FusionXF support ・Air and conduction-cooled variants

-

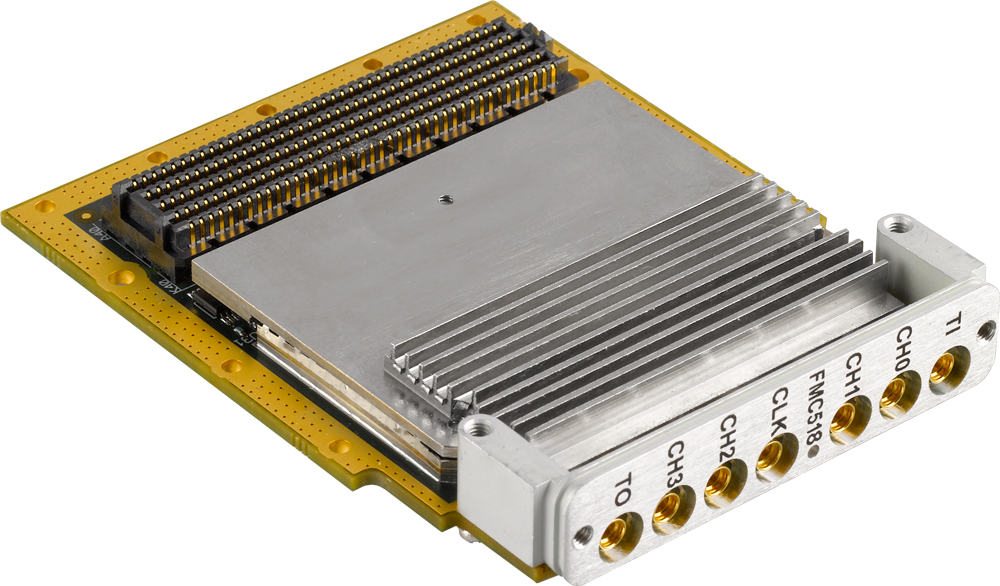

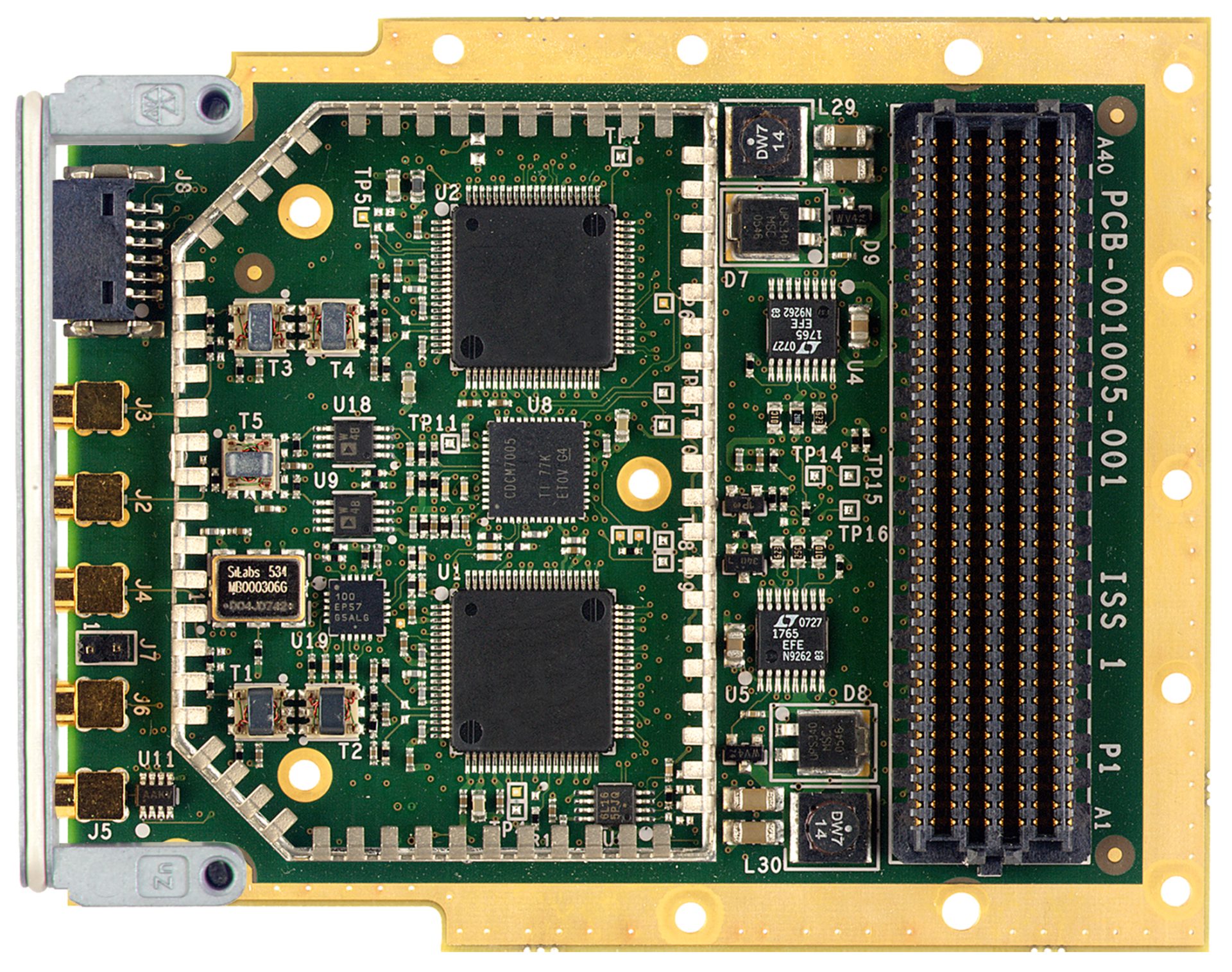

FMC-518 Quad 500MSPS 14b ADC FMC

Curtiss-Wright アナログI/O FMC 防衛・Analog Input: ・Number of Channels: 4, single-ended ・Sampling Frequency: 80 to 500MSPS ・Full Scale Input Voltage: 2V pk-pk ・Device: 4x Intersil ISLA214P50 ・Input Bandwidth (3dB): up to 700 MHz ・Input Impedance: 50 Ohm, AC coupled ・Sample Clock: ・Connector: Front panel MMCX ・Input impedance: 50 Ohm, AC coupled LVPECL ・Clock Input: RF (sample rate) or 10 MHz reference input ・Internal clock selectable from: ・SiLabs Si571 programmable clock (frequency range 80 - 500 MHz) ・Programmable clock source (10MHz - internal or external) ・Configure by FPGA ・Software/HDL Code: ・FusionXF software/HDL tools for Xilinx Virtex-5/6 hosts ・Environmental: ・Ruggedization levels: Air-cooled level 0 and level 100, conduction-cooled level 200

-

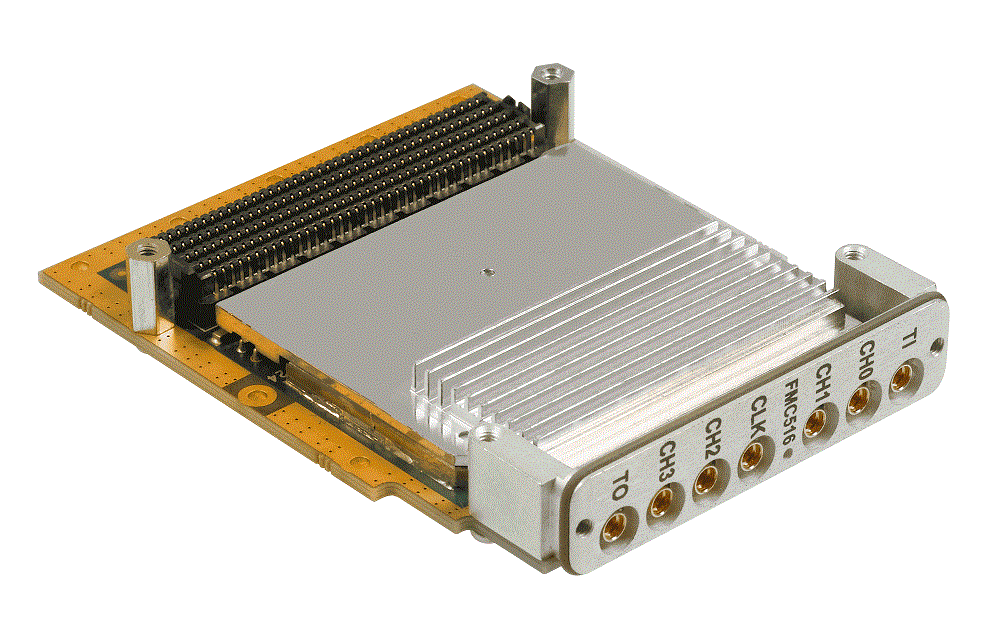

FMC-516 Quad 250MSPS 16b ADC FMC

Curtiss-Wright アナログI/O FMC 防衛・Analog Input: ・Number of Channels: 4, single-ended ・Sampling Frequency: Up to 250MSPS ・Full Scale Input Voltage: 18.8 dBm ・Device: 4x Intersil ISLA216P25 ・Input Bandwidth (3dB): up to 500 MHz ・SFDR (at 105 MHz): 84 dBFS (typ) ・SNR (at 105 MHz): 70 dBFS (typ) ・ENOB (at 105 MHz): 11.3 bits (typ) ・Input Impedance: 50 Ohm, AC coupled ・Input Connector: Front panel MMCX ・Sample Clock: ・Connector: Front panel MMCX ・Input impedance: 50 Ohm, AC coupled LVPECL ・Clock Input: 40-250 MHz (RF) or 10 MHz reference input ・Internal clock selectable from: ・SiLabs Si571 programmable clock (frequency range 40 - 250 MHz) ・Programmable clock source (10MHz - internal or external) ・Configure by FPGA ・Software/HDL Code: ・FusionXF software/HDL tools for Xilinx Virtex-5/6 hosts ・Environmental: ・Ruggedization levels: Air-cooled level 0 and level 100, conduction-cooled level 200

-

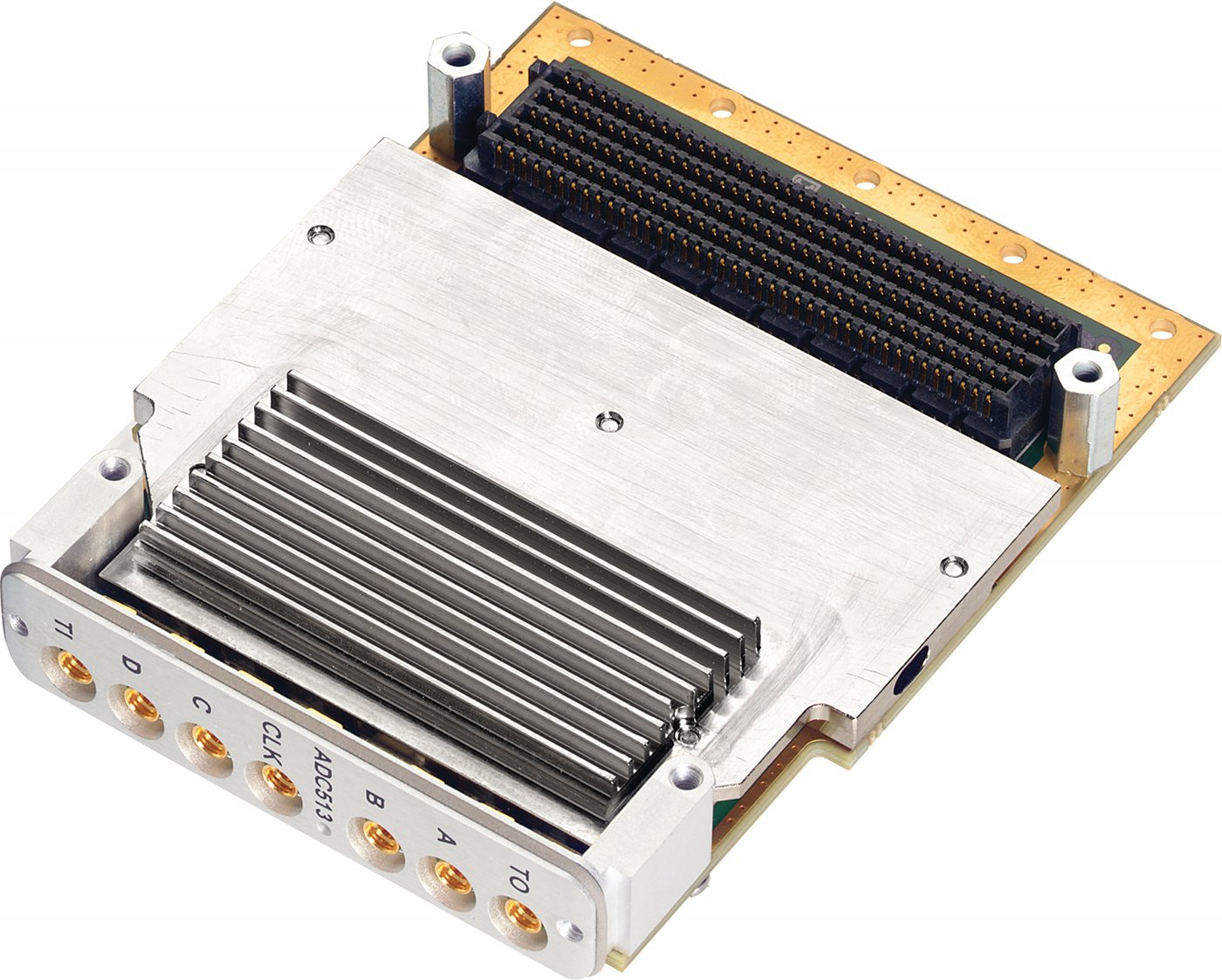

ADC513 Quad 1.5GSPS 8b ADC FMC

Curtiss-Wright アナログI/O FMC 試験 環境・Quad Channel 1.5 GSPS 8-bit ADC FPGA Mezzanine Card (FMC) ・Dual National Semi ADC08D1520, 2-Ch, 8-bit ADCs ・Up to 1.5 GSPS ・AC coupled analog input bandwidth >2.0GHz ・Multi-board synchronization capability ・FMC/VITA 57 (draft) form factor ・FusionXF support ・Air and conduction-cooled variants

-

ADC512 Dual 3GSPS 8b ADC FMC

Curtiss-Wright アナログI/O FMC 試験 環境・Dual Channel 3 GSPS 8-bit ADC FPGA Mezzanine Card (FMC) ・Dual National Semi ADC083000, 8-bit ADCs ・Up to 3 GSPS ・AC coupled analog input bandwidth >2.25GHz ・Multi-board synchronization capability ・FMC/VITA 57 (draft) form factor ・FusionXF support ・Air and conduction-cooled variants

-

ADC511 Dual 400MSPS 14b ADC FMC

Curtiss-Wright アナログI/O FMC 試験 環境・Dual Texas Instruments ADS5474, 14-bit ADCs ・Up to 400 MSPS ・AC coupled analog input bandwidth >1.2GHz ・Choice of onboard and external clocks sources ・Multi-board synchronization capability ・FMC/VITA 57 form factor ・FusionXF support ・Air and conduction-cooled variants