条件に該当する製品96件

-

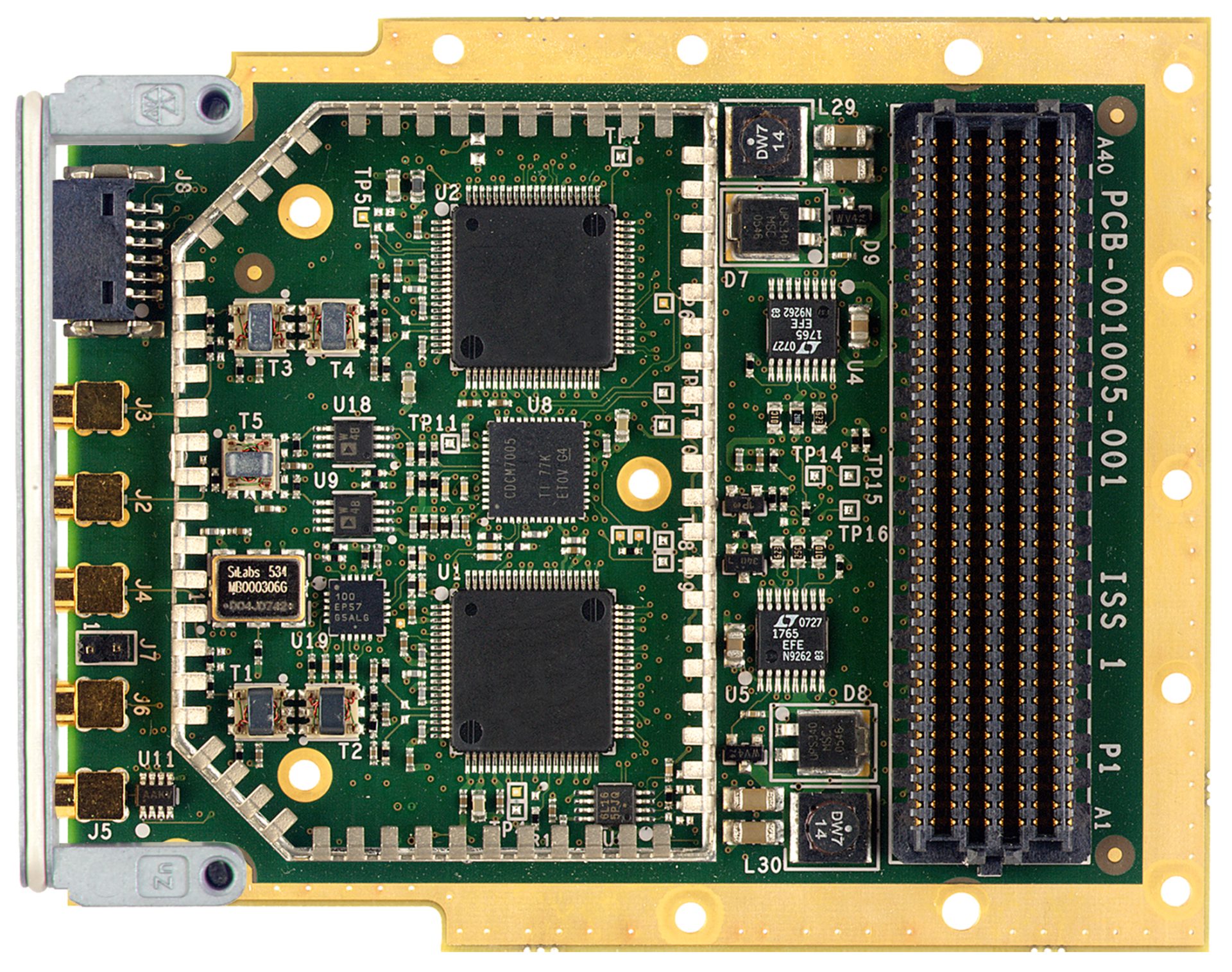

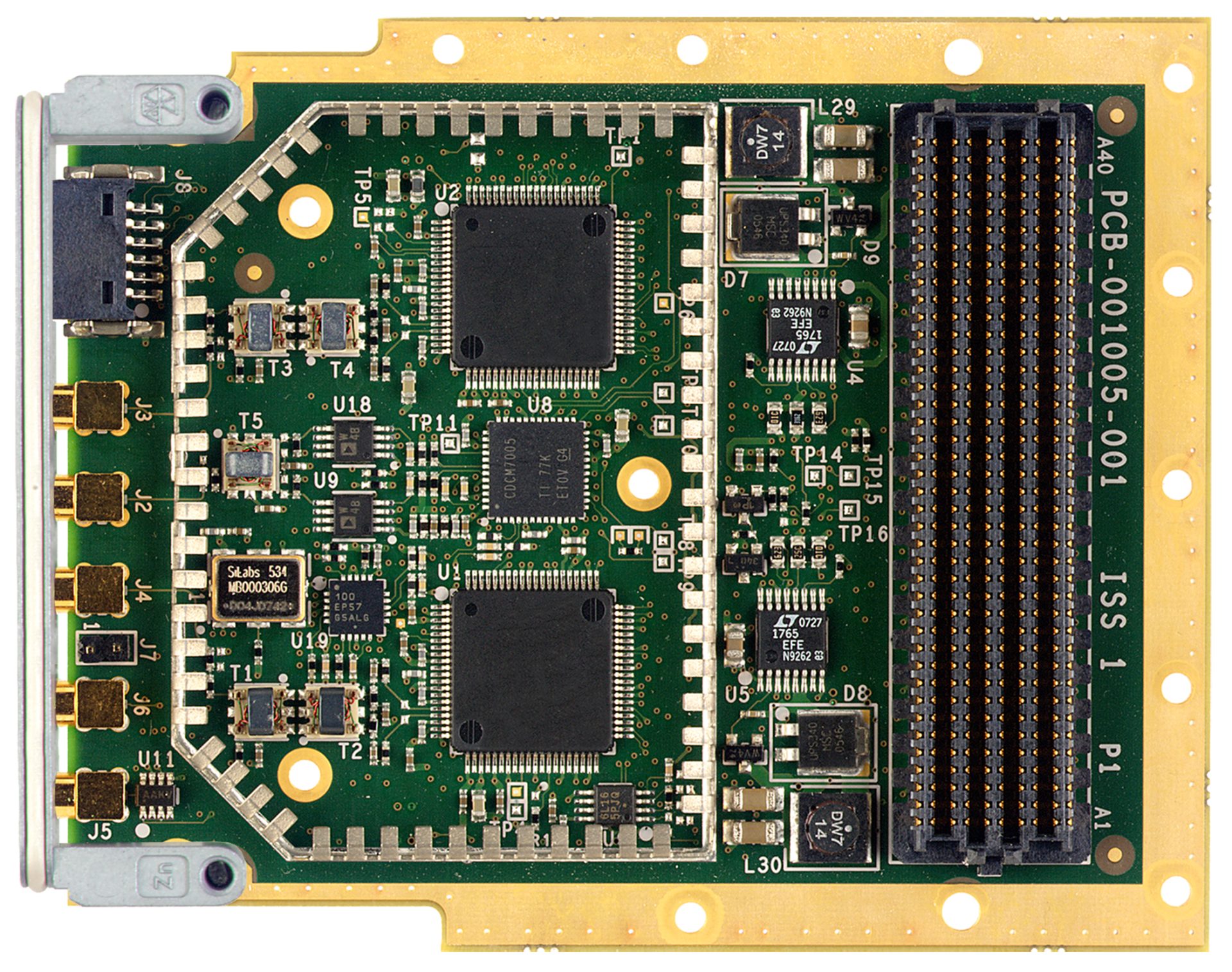

ADC512 Dual 3GSPS 8b ADC FMC

Curtiss-Wright アナログI/O FMC 試験 環境・Dual Channel 3 GSPS 8-bit ADC FPGA Mezzanine Card (FMC) ・Dual National Semi ADC083000, 8-bit ADCs ・Up to 3 GSPS ・AC coupled analog input bandwidth >2.25GHz ・Multi-board synchronization capability ・FMC/VITA 57 (draft) form factor ・FusionXF support ・Air and conduction-cooled variants

-

ADC511 Dual 400MSPS 14b ADC FMC

Curtiss-Wright アナログI/O FMC 試験 環境・Dual Texas Instruments ADS5474, 14-bit ADCs ・Up to 400 MSPS ・AC coupled analog input bandwidth >1.2GHz ・Choice of onboard and external clocks sources ・Multi-board synchronization capability ・FMC/VITA 57 form factor ・FusionXF support ・Air and conduction-cooled variants

-

ADC510 Dual 550MSPS 12b ADC FMC

Curtiss-Wright アナログI/O FMC 試験 環境・Analog Input: ・Number of Channels 2, single-ended ・Sampling Frequency Up to 550MSPS ・Full Scale Input Voltage 2V2 pk-pk ・Device 2x TI ADS5463/ADS54RF63 ・Input Bandwidth (3dB) >1.7GHz ・Input Impedance 50 Ohm, AC coupled ・SNR (device) 65 dBFS ・SFDR (device) 73 dBc ・ENOB (device) 10.1 bits at 250MHz ・Clock & Trigger Inputs: ・Clock Input Connector Front panel MMCX ・Clock Input 50 Ohm, AC coupled LVPECL ・Clock Input Frequency Sample rate is half input clock frequency (i.e. 1GHz for 500MSPS) ・Internal clock selectable from: ・600MHz: 300MSPS ・640MHz: 320MSPS ・800MHz: 400MSPS ・1000MHz: 500MSPS ・Trigger Input/Output Single-ended, 50 Ohm, LVPECL buffered to host FPGA ・Miscellaneous: ・LEDs 2x yellow (host FPGA controlled) ・Digital I/O 4 differential pairs ・Software/HDL Code: ・Host HDL Code Analog input hosted by our FusionXF suite on FPE650 6U quad FPGA VPX (contact Sales for other hosts) ・Environmental: ・Ruggedization levels Air-cooled, air-cooled rugged and conduction-cooled

-

LVDS-MOD4 64x LVDS module

Curtiss-Wright デジタルI/O FMC 試験 環境製品カテゴリ デジタルI/O フォームファクタ PMC/XMC ・Low Voltage Differential Signaling (LVDS) - PMC Front Panel Mezzanine Module ・134 I/O lines routed as 64 differential pairs ・152-pin front panel connector ・Mixed voltage signalling ・FPGA Firmware blocks supplied in VHDL for integration into user applications ・Windows, VxWorks and Linux host PMC support

-

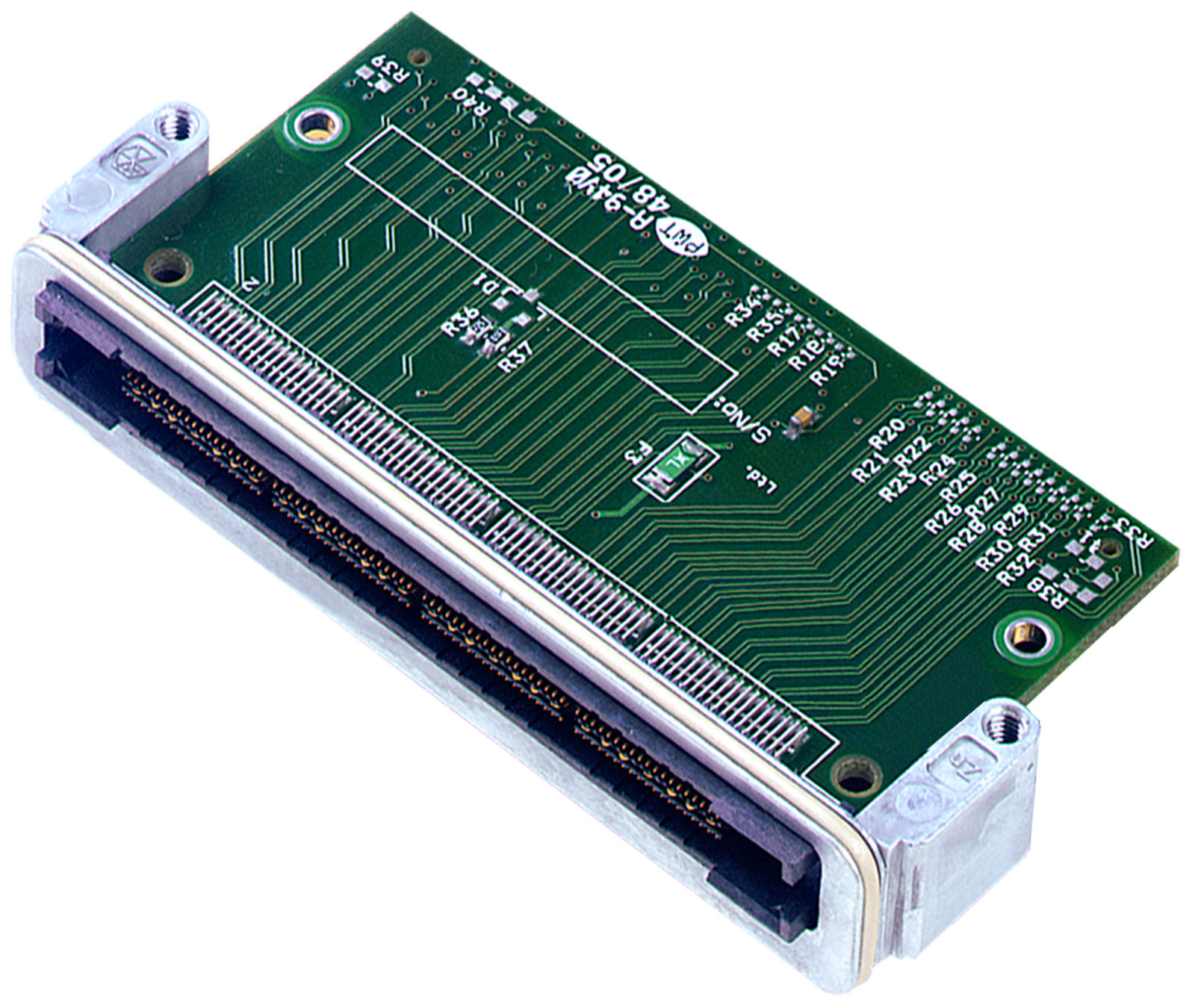

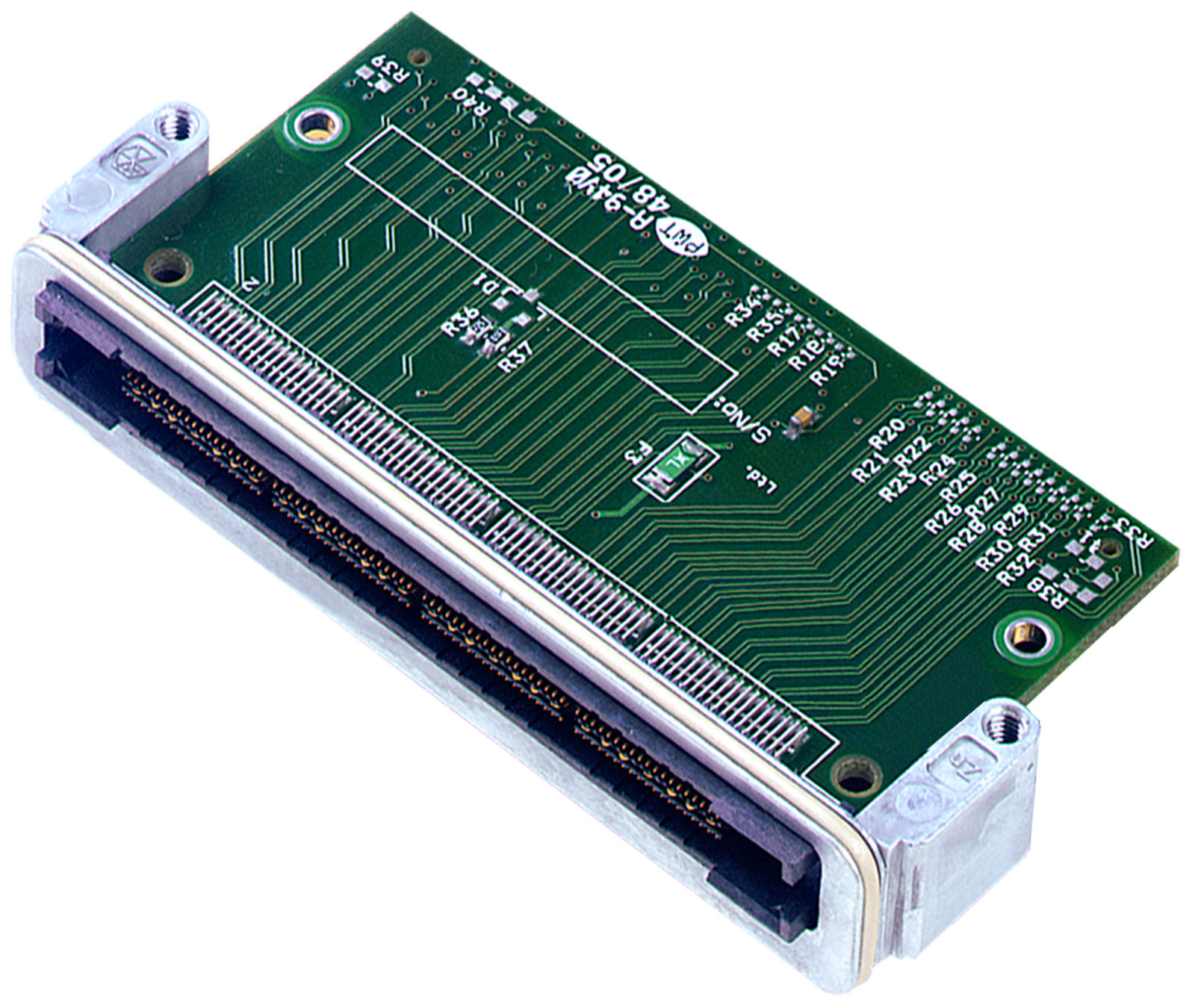

LVDS-MOD3 32x LVDS module

Curtiss-Wright デジタルI/O FMC 試験 環境製品カテゴリ デジタルI/O フォームファクタ PMC/XMC ・64 I/O lines routed as 32 differential pairs ・68-way SCSI-3 style front panel connector ・Mixed voltage signalling ・FPGA Firmware blocks supplied in VHDL for integration into user applications ・Windows, VxWorks and Linux host PMC support

-

DAC-MOD1 Dual 210MSPS, 14-bit DAC

Curtiss-Wright アナログI/O FMC 防衛製品カテゴリ アナログI/O フォームファクタ ・Front Panel Analog Signal Input ・Number of Channels: 2 (single ended) ・Connectors: AC coupled, front panel MMCX connector ・Full Scale Output: 0.5V pk-pk into 50 ohms ・Output Impedance: 50 ohms ・D/A Converter ・Quantity: 1 ・Type: Analog Devices AD9744 ・Sampling Rate: 210MSPS ・Resolution: 14 bits ・SNR @ 5 MHz output, 125MSPS: 77dB ・External Clock Input ・Connector: Front Panel MMCX ・Input Level: 1V pk-pk, sine or squarewave ・Input Impedance: 50 Ohms, AC coupled LVPECL ・Clock Selection: Controlled by FPGA ・Trigger ・Single-ended, 50 Ohm, DC coupled

-

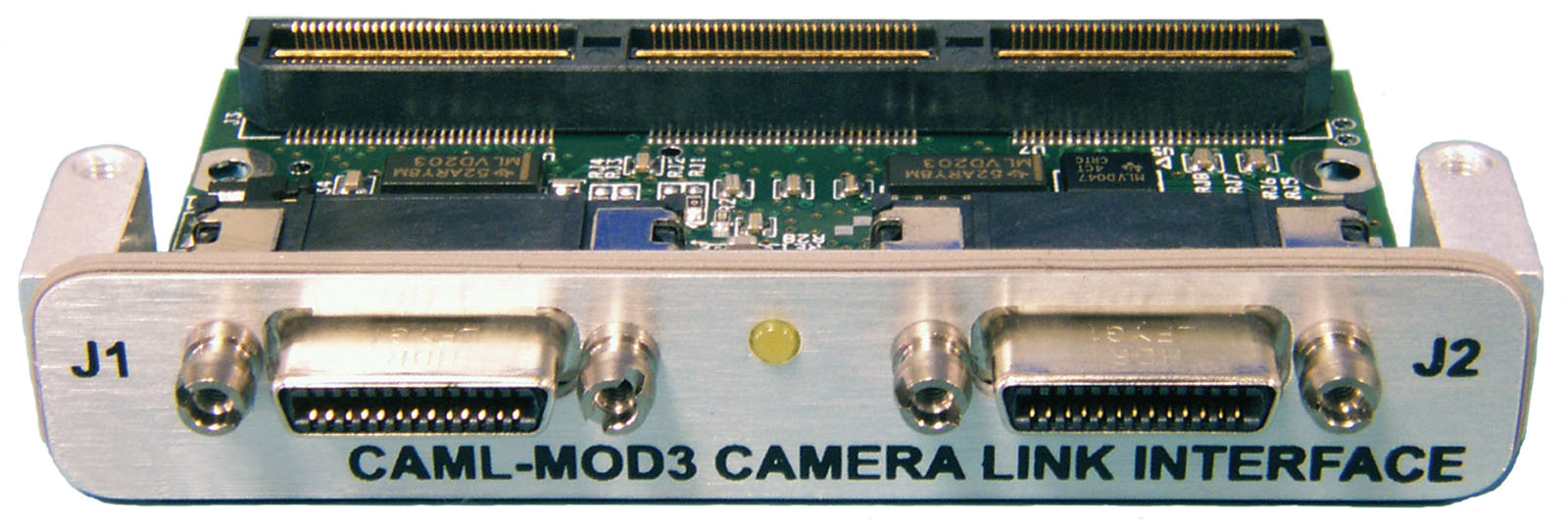

CAML-MOD3 CameraLink module

Curtiss-Wright ビデオ FMC 防衛製品カテゴリ デジタルI/O フォームファクタ PMC/XMC ・CameraLink - PMC Front Panel Mezzanine Module ・Supports Base, Medium and Full mode Camera Link implementations ・Up to 85 MHz Camera Link clock rate ・Up to two cameras in Base mode, or one camera in Medium or Full mode ・Two Mini Camera Link interface connectors ・Fully documented example firmware and software with complete source code

-

ADC-MOD2 125 MSPS 14-bit ADC

Curtiss-Wright アナログI/O FMC 物理 天体製品カテゴリ アナログI/O フォームファクタ ・Front Panel Analog Signal Input: ・Number of Channels 2 ・Connectors AC coupled, frontpanel MMCX connector ・Full Scale Input +10 dBm (2V pk-pk) into 50 ohms ・SNR 68dB ・SFDR 82dB ・A/D Converter: ・Quantity 1 ・Type Linear Technology LTC2285 ・Sampling Rate 125MSPS ・Resolution 14 bits ・Bandwidth 100kHz to 110MHz full power bandwidth ・External Clock Input: ・Connector Front Panel MMCX ・Input Level 200 - 1000 mV pk-pk, sine or squarewave ・Input Impedance 50 Ohms, AC coupled LVPECL ・Clock Selection Controlled by FPGA ・Trigger: ・Single-ended, 50 Ohm, DC coupled

-

FMC117(Quad zSFP+/SFP28 (protocol agnostic)

VadaTech 光/SFP/QSFP他 FMC 物理 天体FPGA Mezzanine Card (FMC) compatible with VITA 57.1 •Four zSFP+/SFP28 cages •Onboard Fractional PLL to generate any clock •Protocol agnostic (i.e. 5GbE, 10Gb, 28G, Aurora, etc.)

-

FMC116(Octal zSFP+/SFP28 (protocol agnostic)

VadaTech 光/SFP/QSFP他 FMC 物理 天体FPGA Mezzanine Card (FMC) compatible with VITA 57.1 •Eight zSFP+/SFP28 cages •Onboard Fractional PLL to generate any clock •Protocol agnostic (i.e. 5GbE, 10Gb, 28G, Aurora, etc.)